«ANALYSE ET MÉCANISMES DE DÉFAILLANCE DES COMPOSANTS POUR L'ÉLECTRONIQUE »

Village Club Belambra « Les Tuquets »

Seignosse - Hossegor (Landes) - France

7 juin au 10 juin 2016

**ORGANISE PAR**

Association Ioi 1901

Analyse de défaillance & technologie des composants électroniques www.anadef.org

avec le concours de

# **PROGRAMME DES SESSIONS PLENIERES**

## MARDI 7 JUIN

Alain WISLEZ

Président Association ANADEF alain.wislez@thalesgroup.com Tél : 05 62 88 28 04

14h00 - 18h00

Animateurs:

Olivier MAIRE

AIRBUS Group Innovations - Suresnes olivier.maire@airbus.com Tél : 01 46 97 37 61

Julien PERRAUD

THALES R&T - Palaiseau julien.perraud@thalesgroup.com Tél : 01 69 41 56 70

Frédéric DULONDEL

SAGEM Défense Sécurité - Eragny frederic.dulondel@sagem.com Tél : 01 58 11 93 89 8h30 9h30 - 10h00 Accueil des participants

Ouverture et présentation de l'atelier 2016

# Session n°1

# « Assemblages et packaging »

Plus petite, plus puissante et consommant moins ; chaque nouvelle génération se doit d'être plus performante. Du fait des limites sans cesse plus complexes à repousser pour les VLSI, le packaging participe maintenant pleinement à cette course à l'intégration. Il en va de même pour les PCB et l'assemblage avec une diminution constante des pas ou encore pour les connecteurs qui doivent permettre des débits de plus en plus élevés.

Cette session nous donnera l'occasion de regarder l'impact de ces développements sur les assemblages, les boîtiers de composants, les circuits imprimés, ainsi que les techniques d'analyse associées.

Nous voulons, cette année, mettre particulièrement l'accent sur les boîtiers SiP/MCM, les PCB HDI et les connecteurs. Pour chaque cas, seront présentés, les mécanismes de défaillance et les méthodes de caractérisation associées, qu'il s'agisse de nouvelles techniques d'analyse ou de l'adaptation de techniques existantes.

Cette session permettra également de présenter les travaux menés par les groupes de travail ANADEF qui adressent les assemblages sans Plomb et les PCB.

## **MERCREDI 8 JUIN**

14h00 - 18h00

Animateurs :

#### Alain WISLEZ

THALES C&S - Toulouse alain.wislez@thalesgroup.com Tél : 05 62 88 28 01

#### Catherine MUNIER

AIRBUS Group Innovations - Suresnes catherine.munier@airbus.com Tél : 01 46 97 35 03

#### David LOHIER

HIREX Engineering - Toulouse d.lohier@hirex.fr Tél: 05 62 47 56 90

# Session n°2

# « Analyse de défaillance des composants de puissance »

Les composants de puissance sont plus que jamais incontournables. Les applications sont multiples : le transport, l'énergie, la conversion d'énergie, l'éclairage, le spatial, le militaire, ... Les composants électroniques de puissance n'ont jamais connu autant d'évolutions technologiques que ces dernières années. Poussés par leurs clients, les fabricants de composants conçoivent des composants plus performants, plus fiables, plus spécifiques, plus économes en énergie, plus respectueux de l'environnement et de la santé de l'utilisateur et surtout moins cher!

Ces évolutions sont possibles grâce à des révolutions technologiques tant au niveau de la puce que du boîtier. Aucune partie du composant n'est laissée de côté :

- les substrats de la puce (Si, SiC, GaN pour les technologies commercialisées, Diamant, ... pour les technologies en cours de développement),

- les pistes métalliques (Al, AlCu, AlSiCu, Cu, autres ??) et les diélectriques High K et Low K,

- les designs en 3D,

- les assemblages des puces (colles, brasures, frittage de poudre, wire bondings, ribbon bondings, copper-pillars, autres),

- les résines de boîtiers, les assemblages complexes en modules, et les PCBs.

Les nouveaux composants de puissance doivent être aussi bien caractérisés et fiabilisés que les anciens.

Les mécanismes de défaillance des composants de puissance sont dorénavant aussi divers que variés. Le simple « burn out » n'est plus une explication suffisante et nécessaire ; ce n'est qu'une résultante d'une suite d'événements au sein du matériau ou de la structure. L'analyse de défaillance des composants de puissance nécessite la mise en œuvre d'une très large palette de moyens au même titre que pour les technologies les plus agressives ou très intégrées ainsi que la mise au point des techniques préalablement utilisées (par exemple la coupe micrographique).

Cette session aura donc pour objectif de faire un tour d'horizon de ces nouveaux composants de puissance, des mécanismes de défaillances et des méthodes d'analyse associées.

# PROGRAMME DES SESSIONS PLENIERES

# JEUDI 9 JUIN

#### 8h30 - 12h00

Animateurs:

#### Suzel LAVAGNE

THALES C&S - Toulouse suzel.lavagne@thalesgroup.com Tél : 05 61 88 75 83

### Kevin SANCHEZ

CNES - Toulouse kevin.sanchez@cnes.fr Tél : 05 61 27 31 78

#### **Gerald HALLER**

STMicroelectronics - Rousset gerald.haller@st.com Tél : 04 42 68 55 78

# Session n°3

# « Analyse de défaillance des circuits intégrés »

Reste-t-il encore de l'analyse de défaillance sur les VLSI en France? Telle est la question que l'on peut se poser compte tenu des évolutions économiques de ces dernières années. Cette session aura pour but de démontrer que les compétences sont encore là, et qu'elles se développent en fonction des besoins.

Deux tendances se détachent de plus en plus nettement dans ce domaine.

D'un côté les fondeurs, qui réalisent des prouesses techniques repoussant sans cesse les limites de la détection, entrainant les fabricants de matériel dans leur course contre le nanomètre. L'évolution des matériaux dans des nœuds inférieurs à 65nm, met au centre du défi, les techniques de nanoprobing (et techniques dérivées) et augmente l'influence des outils d'analyses physiques tels que le FIB, le TEM, l'AFM et les techniques dérivées EBIC et EBAC.

Ces fondeurs bénéficient des informations de conception, de fabrication ainsi que des résultats de test pendant la conception qui leur permettent d'intervenir dès la conception du circuit. Les campagnes de qualification des technologies sont les briques de base aux simulations de comportement des produits ; l'orientation de l'analyse de défaillance s'en trouve alors très ciblée avec une probabilité de résultat importante. La traque du « soft defect » poussent les fabricants à utiliser de nouvelles techniques de localisation électro-optiques dans lesquelles les « Solid Immersion Lens» sont devenues incontournables.

D'un autre côté, les intégrateurs doivent relever le défi de travailler dans une situation d'urgence avec une approche boite noire. La question récurrente étant : est-ce un défaut de fabrication ou d'utilisation ? Ces fabricants ont besoin de techniques rapides, peu invasives, peu onéreuses et qui permettent d'analyser des surfaces importantes. Des techniques, telles que le LIT « Lock in Thermography », atteignent un niveau de maturité élevé; pour d'autres, les applications débutent (Time Resolved imaging, Laser Voltage Imaging...). La difficulté de ces analyses réside dans les hypothèses à prendre en phase initiale qui pourront influencer le verdict final, la démarche tout au long de l'analyse étant la clé de la réussite.

Enfin, un dernier pan du VLSI et indirectement de l'analyse de défaillance concerne les interactions laser/puce ou comment créer des défauts avec un laser pour créer des défauts dans des produits sécurisés ou simuler des défauts dans les composants spatiaux.

Cette session sera l'occasion de présenter : les nouvelles techniques, les techniques les plus couramment utilisées, les défis techniques et économiques liés à ces analyses, ce que l'on peut faire quand on a peu d'outils ou peu de connaissances sur le produit, les tendances actuelles (outils logiciels, Design for FA ...).

## 14h00 - 17h30

#### Animateurs:

#### Matthieu GLEIZES

MBDA France - Le Plessis Robinson matthieu.gleizes@mbda-systems.com Tél : 01 71 54 36 20

#### Dominique TALBOURDET

EDF R&D - Moret-sur-Loing dominique.talbourdet@edf.fr Tél: 01 60 73 63 91

#### Christian MOREAU

DGA - Maîtrise de l'information christian.moreau@intradef.gouv.fr Tél : 02 99 42 93 98

#### Marise BAFLEUR

LAAS / CNRS - Toulouse marise@laas.fr Tél: 05 61 33 69 66

# Session n°4

# « Défiabilisation des composants en utilisation »

Les composants électroniques sont de plus en plus fiables mais également de plus en plus fragiles, et donc sensibles aux stress. Le taux de panne, proche du zéro défaut à réception augmente brutalement dès qu'ils sont intégrés dans une application. Dans de nombreux cas, la cause racine de ces pannes est une mise en œuvre inappropriée: conditionnement inadapté, mauvaise gestion du MSL, procédés de fabrication et test mal maîtrisés, utilisation client en dehors des limites garanties, stockage de longue durée, etc. Beaucoup de ces stress induits vont également générer des défauts latents qui ne seront pas détectés par les contrôles. Il est donc capital pour l'industriel de savoir identifier ces causes de défiabilisation.

La difficulté majeure pour l'expert est l'identification des causes racines de la défaillance car il s'agit en général de stress «parasites» donc hors processus nominal et souvent accidentels. D'autres évènements peuvent générer un défaut latent non détectable lors d'un test fonctionnel mais susceptible d'évoluer au cours de la vie du composant. Outre ces stress parasites, un composant peut aussi se dégrader au cours d'une utilisation particulièrement longue comme c'est le cas dans les domaines militaires, aéronautiques et production d'énergie. L'objectif de cette session est de partager les expériences de chacun en balayant toutes les étapes de vie d'un composant du déstockage magasin à l'utilisation du matériel par le client. Les présentations seront orientées sur plusieurs axes :

- Études de cas ayant une signature particulière et si possible la cause bien identifiée,

- Mécanismes de défaillance liés à l'évolution des technologies et aux nouveaux procédés.

- Exemples montrant la relation entre les stress induits par le procédé industriel ou l'application elle-même (température, ESD, EOS, EMI, rayonnement cosmique, contraintes électromagnétiques, fissures de boîtiers, délaminations, pollutions, etc.) et la fiabilité à long terme. Sensibilité de la conception système aux perturbations transitoires, entraînant une défiabilisation au niveau composant.

# VENDREDI I O JUIN

## 8h30 - 10h00

Animateurs:

#### Gérald GUIBAUD

Thales C&S - Toulouse gerald.guibaud@thalesgroup.com Tél : 05 61 28 16 95

### Lionel DANTAS de MORAIS

SOFRADIR - Veurey Voroize lionel.dantasdemorais@sofradir.com Tél : 04 76 28 89 38

#### Claire VACHER

ULIS - Veurey Voroize c.vacher@ulis-ir.com Tél : 04 76 53 68 17

# Session n°5

# « Analyse de défaillance des composants optoélectroniques »

Depuis quelques années, les produits électroniques intègrent de plus en plus de fonctionnalités nécessitant l'utilisation de composants dits « optoélectroniques », aussi bien dans les applications dites « grand public » (téléphone, tablette, console de jeu, système domotique...) que dans les secteurs aéronautique, spatial ou militaire. Ces composants vont capter ou émettre un rayonnement photonique dont la longueur d'onde variera selon les cas. Nous retrouvons parmi ces composants les photodiodes, les photomultiplicateurs, les photorésistances, les photorransistors, les cellules photoélectriques, les diodes laser/électroluminescentes, les micro-bolomètres etc...

Ces technologies utilisent de nouveaux types de composants actifs dont les modes de défaillances vont être différents de ceux rencontrés jusqu'à présent dans le domaine de la microélectronique classique (VLSI, CMOS etc...). Par conséquent, les techniques d'analyse de défaillances ont dû évoluer pour s'adapter à ces nouveaux modes de défaillances d'un point de vue caractérisation électro-optique, localisation de défauts, définition des nouvelles sources de défauts, compatibilité des analyses avec les nouveaux matériaux...

L'objectif de cette session est de partager des cas de défaillances sur composants optoélectroniques et d'en détailler les processus d'analyse et les techniques de tests électro-optiques, la recherche de défauts associés ayant permis d'aboutir à la résolution du problème initial.

## PROGRAMME DES TUTORIELS

## MARDI 7 JUIN

10h00 - 12h00 14h00 - 15h30

#### Gerald HALLER

STMicroelectronics - Rousset gerald.haller@st.com Tél : 04 42 68 55 78

# Tutoriel 1 « Les fondamentaux de l'analyse de défaillances »

L'analyse de défaillance des composants est un processus complexe mettant en œuvre différentes techniques d'analyse et d'observation. Bien que certaines techniques aient évolué pour répondre aux défis amenés par la miniaturisation des composants aussi bien en termes dimensionnels que du fait de l'intégration hétérogène des technologies de fabrication, le « flot d'analyse de défaillance » et la plupart des techniques restent des fondamentaux.

Le tutoriel se propose de parcourir le flot d'analyse standard en partant de la collecte des informations relatives à la défaillance du composant jusqu'à la détermination de son mécanisme de défaillance. Chaque étape du processus permettra d'introduire les différentes techniques qui sont à disposition de l'analyste afin de progresser dans la recherche du défaut :

- Analyse non destructive (Xrays, SAM, Microscopie optique ...)

- Localisation de la défaillance (EMMI, OBIRCH, Thermographie, LVP, EBT, TRE ...)

- Observation et caractérisation du défaut (SEM, TEM, Auger, EDX ...

Lors de chaque étape d'analyse, les différentes méthodes de préparation des échantillons (ouverture du boitier, microsection FIB, polissage ...) qui sont primordiales dans la réussite d'une analyse seront aussi abordées.

# **MERCREDI 8 JUIN**

#### 8h30 - 12h00

#### Pascal GOUNET

STMicroelectronics - Grenoble pascal.gounet@st.com Tél: 04 76 58 60 17

#### Luc SAURY

STMicroelectronics - Grenoble luc.saury@st.com Tél: 04 76 58 66 57

# **Tutoriel 2** « Analyse de défaillances avancée : localisation et observation de défauts dans les VLSI »

Les défauts rencontrés dans les technologies VLSI avancées actuelles sont-ils localisables ? Analysables ? Quel processus d'analyse et quels outils peuvent être mis en œuvre ? L'objectif ambitieux de ce tutoriel est de vous aider à répondre à ces questions.

L'analyse de défaillance consiste à rechercher le défaut physique responsable du défaut électrique. Elle comprend trois étapes principales: la caractérisation électrique, la localisation du défaut puis l'analyse physique qui mène à l'identification du défaut et le cas échéant précise l'origine de son apparition.

Ce tutoriel adresse de manière plus spécifique la localisation des défauts et comporte 3 parties :

- Mécanismes de défaillance dans les technologies actuelles Signature électrique et physique des défauts (visibles ou non-visibles),

- Processus de l'analyse de défaillances et outils adaptés aux technologies actuelles, du diagnostic à la localisation,

- Techniques optiques de localisation de défauts: cette partie concerne les techniques statiques et dynamiques de thermographie, d'émission de lumière, de stimulation Laser et de Laser en mode réfléchi avec comme objectif de préciser quelle technique choisir et pourquoi.

## JEUDI 9 JUIN

#### 8h30 - 12h00

### Yannick DESHAYES

Laboratoire IMS -Université de Bordeaux yannick.deshayes@ims--bordeaux.fr Tél : 05 40 00 27 68

# **Tutoriel 3** « Analyse de défaillance des LEDs et des diodes Laser »

Les composants optoélectroniques émissifs LEDs et Diodes Laser sont utilisés dans l'industrie depuis la fin des années 70 pour des applications de télécommunication (fibre optique) ou bien des dispositifs de détection ou de télécommande (LED). Le domaine de longueur d'onde privilégié était l'infrarouge (870 nm - 1550 nm). Depuis le début des années 90, la LED bleu est apparue et a permis le développement de sources de lumière blanche.

Dans le premier cours, nous balayerons le fonctionnement des composants LEDs et Diodes laser et nous nous focaliserons sur le parallèle matériau - fonction. Les caractérisations électro-optiques seront abordées afin d'introduire le second cours sur l'analyse de défaillance de composants LEDs et DL.

Les phénomènes de dégradation des composants LEDs et DL sont fortement dépendants de la filière technologique : GaAs, InP, GaP ou GaN. La maîtrise de l'épitaxie permet aujourd'hui de réduire la densité de défauts à des niveaux comparables aux technologies silicium. La puce est donc assez peu défaillante dans les systèmes modernes, mais l'un des points d'amélioration est centré sur l'assemblage. Les composants optoélectroniques souffrent également de mécanismes de défaillance qui leur sont propres : la dégradation de la partie optique. Nous verrons donc les méthodes d'analyse non destructive permettant de discriminer la défaillance venant du composant de celle venant de l'assemblage. Nous donnerons plusieurs exemples d'analyse de défaillance par simulation 3D, extrapolation de durée de vie par tirage Monte Carlo, analyses physicochimiques,...

## VENDREDI I O JUIN

#### 8h30 - 12h00

#### Françoise GONNET

THALES R&T - Palaiseau francoise.gonnet@thalesgroup.com Tél : 01 69 41 56 68

#### Matthieu GLEIZES

MBDA France - Le Plessis Robinson matthieu.gleizes@mbda-systems.com Tél : 01 71 54 36 20

#### Cécile PLOUZEAU

RENAULT - Guyancourt cecile.plouzeau@renault.com Tél : 01 76 85 09 73

# **Tutoriel 4** « Composants passifs : technologies et analyse de défaillances »

Les composants passifs représentent bien souvent 80% du nombre de composants d'une carte électronique et à peine 10% du prix de cette carte. Certes ces composants ne sont pas les "locomotives" des assemblages, mais sans passifs rien ne serait actif !!

Ils sont souvent sacrifiés pour protéger les composants actifs car il est plus facile et moins onéreux de changer un passif qu'une mémoire ou un processeur. De ce fait les composants passifs sont à l'origine de 30% des défaillances des cartes électroniques.

Il est très difficile de réaliser une analyse de défaillance sur un composant sans connaître son procédé de fabrication, ni ses faiblesses. Il faut un minimum de connaissances pour localiser le défaut et réaliser l'analyse physique qui mène à l'identification du défaut , voire à son origine.

Ce tutoriel a pour objectif de vous présenter 4 familles de composants : les condensateurs, les résistances, les inductances et transformateurs, les relais électromécaniques.

Pour chaque famille seront présentés les principales technologies, les principaux modes et mécanismes de défaillance. Nous vous présenterons des cas d'analyses de défaillances qui serviront également de support pour vous parler des différentes techniques d'analyses qui peuvent être utilisées.

# **PROGRAMME DES MICRO-ATELIERS**

Ces « micro-ateliers » ont pour objectif de favoriser les échanges informels entre les analystes de défaillance. Chaque « micro-atelier » comprendra une description rapide du thème suivi d'études de cas montrant des exemples d'utilisation. L'étude de ces cas permettra de décrire des problèmes résolus ou non et de présenter la méthode employée pour traquer un défaut. A l'issue de ces présentations, un débat entre les participants pourra donner lieu à des discussions qui favoriseront l'échange et le partage d'expériences.

## MARDI 7 JUIN

#### 10h00 - 12h00

#### Animateurs:

### Dominique CARISETTI

THALES R&T - Palaiseau dominique.carisetti@thalesgroup.com Tél : 01 69 41 56 73

#### Frédéric BOURCIER

CNES - Toulouse frederic.bourcier@cnes.fr Tél : 05 61 28 17 71

#### Vincent GOUBIER

STMicroelectronics - Rousset vincent.goubier@st.com Tél : 04 42 68 51 60

# 16h00 - 18h00

#### Animateurs:

#### Lionel DANTAS de MORAIS

SOFRADIR - Veurey Voroize lionel.dantasdemorais@sofradir.com Tél : 04 76 28 89 38

#### Fulvio INFANTE

INTRASPEC - Technologies fulvio.infante@intraspectechnologies.com Tel :05 61 27 45 54

#### Claire VACHER

ULIS - Veurey Voroize c.vacher@ulis-ir.com Tél : 04 76 53 68 17

# Micro-atelier n°1 « Mesures et caractérisations thermiques »

La gestion de la thermique est un élément clé qui doit être pris en compte dans les systèmes électroniques. La fiabilité des matériels à 10 voire 20 ans impose une maîtrise de la température des composants sans sur-dimensionner le refroidissement. La connaissance la plus précise possible de la température de jonction est primordiale pour calculer efficacement les échanges de chaleur et le MTTF. Ce micro-atelier permettra d'aborder les différentes techniques de mesures thermiques directes ou indirectes utilisées en industrie ou dans le domaine académique sur les composants Silicium et III-V (composant de puissance, diode laser...) à l'échelle micrométrique et nanométrique.

- Techniques électriques et optoélectroniques (à l'échelle du composant) : Mesure du décalage de la tension de seuil en fonction de la température, Paramètres optoélectroniques (P de I) ou décalage en longueur d'onde.

- Techniques électro-optiques (à l'échelle micrométrique): Cristaux liquides, Thermographie infrarouge, Mesures Raman et photoluminescence, Thermoréflectance.

- Techniques thermo-résistive (échelle nanométrique) : Scanning Thermal Microscope

Nous discuterons des limites de chaque technique en termes de résolution spatiale (X,Y,Z) et de résolution temporelle. Nous aborderons aussi les domaines d'incertitude selon l'échantillon et les matériaux analysés sur la mesure de température absolue pour le calcul de la résistance thermique Rth, et de l'impédance thermique Zth.

# Micro-atelier n°2 « Outils logiciels d'aide à l'analyse de défaillance »

L'analyse de défaillance s'appuie sur des techniques et des équipements de laboratoire très variés. Ce métier est donc très axé « laboratoire » et approche terrain. L'objectif de ce micro atelier est de donner une part plus importante aux logiciels utilisés par les analystes et de présenter leur utilisation dans les laboratoires. Ces « softwares » peuvent être issus de développements « maison » (ex : macro Excel, interface LabView, etc.) ou proposés par des éditeurs spécialisés, en version gratuite ou payante. Ces logiciels peuvent apporter une aide précieuse sur de nombreux domaines :

- Gestion des équipements : réservation, suivi métrologique, maintenance et taux de panne, pilotage à distance, etc.

- · Gestion des analyses : centralisation des demandes, stockage des données, édition et gestion des rapports finaux, etc.

- Traitement de données : comparaison de signaux, reconstruction d'images 2D / 3D, etc.

- Simulation de défauts : simulation de signal électrique et injection de défaut, etc.

- Compréhension des phénomènes physiques : interactions électrons / ions / matière par des modèles Monte Carlo, simulation thermo mécanique par éléments finis, etc.

La liste ci-dessus a volontairement un spectre large mais n'est pas exhaustive. Ce premier micro atelier autour des logiciels doit aussi nous permettre d'avoir un regard nouveau sur la façon de gérer et réaliser nos analyses.

## **MERCREDI 8 JUIN**

#### 8h30 - 12h00

#### Animateurs :

#### Pascal RETAILLEAU

MBDA France - Le Plessis Robinson pascal.retailleau@mbda-systems.com Tél : 01 71 54 26 76

#### Sylvie HEUDE-VERNEYRE

AIRBUS D&S (Astrium) - Elancourt sylvie.heude-verneyre@astrium.eads.net Tél : 01 82 61 25 94

#### Hélène FREMONT

IMS - Bordeaux helene.fremont@ims-bordeaux.fr Tél : 05 40 00 27 65

# **Micro-atelier n°3** « PCB, assemblages et packaging : problématiques d'analyse »

Ce micro-atelier a pour but d'échanger sur les méthodes d'analyse utilisées dans le domaine des PCB, des assemblages et du packaging. Il sera conçu en étroite collaboration avec les animateurs de la session 1 afin de permettre de revenir sur les principaux thèmes absorbés lors de la session, avec une approche plus concrète de ces sujets au sens de l'analyse et de la recherche des mécanismes de défaillance. Il sera également le lieu pour aborder une série de sujets nouveaux comme les MCMs, les connecteurs encartables, l'analyse des assemblages 3D et pour discuter les derniers résultats obtenus avec des techniques d'analyses innovantes comme l'EBSD au service de la caractérisation des alliages SAC, les mesures de micro-déplacement de connecteurs par effet doppler, ....

Ce micro atelier servira aussi de tremplin pour présenter ou introduire les travaux et/ou résultats des GT Sans Plomb, PCB et Vernis. Les sujets seront introduits par de courtes présentations axées sur des études de cas. L'accent sera mis sur le partage de l'expérience des participants, avec le souhait de débattre sur les avantages et inconvénients des différentes techniques et sur les performances des moyens d'analyse.

## PROGRAMME DES MICRO-ATELIERS

## **MERCREDI 8 JUIN**

#### 14h00 - 18h00

#### Animateurs:

Vanessa CHAZAL

THALES C&S - Toulouse vanessa.chazal@thalesgroup.com Tél : 05 61 28 75 28

Djemel LELLOUCHI

ELEMCA - Toulouse djemel.lellouchi@elemca.com Tél: 05 61 27 32 40

# Micro-atelier n°4 « Préparation d'échantillons »

Les échantillons que nous devons analyser sont dans des technologies d'assemblage de plus en plus complexes : SIP, assemblages 3D, TSV, flip chip, COB, MEMS.... Au silicium aux nœuds technologiques de plus en plus fins, s'ajoute les technologies GaAs, GaN, SiC, SiGe et bien d'autres pour générer des objets de plus en plus variés. Comment préparer tous ces échantillons pour pouvoir localiser les défauts ? (accès face avant, face arrière, techniques de repackaging...). L'apparition de nouveaux matériaux (fils en argent, low et high K, BCB...) et la mise en place de la directive européenne REACH induisent des difficultés supplémentaires.

Quelles techniques sont mises en œuvre et quels sont vos retours d'expérience ?

Comment adapter les techniques de delayering, microsection, microscopie en transmission, EBSD, révélations chimiques .... aux nouvelles technologies ? Quels outils ou nouvelles méthodes doit-on mettre en œuvre ?

Ce micro atelier sera un lieu d'échanges et de débats sur les techniques et outils de préparation actuels, les difficultés rencontrées, les astuces et tout ce qui peut intéresser ceux et celles qui sont confrontés aux problématiques de préparation d'échantillon.

# JEUDI 9 JUIN

#### 14h00 - 15h30

#### Animateurs:

#### Kevin SANCHEZ CNES - Toulouse

kevin.sanchez@cnes.fr Tél: 05 61 27 31 78

#### Guillaume BASCOUL

INTRASPEC-Technologies - Toulouse guillaume.bascoul@intraspectechnologies.com

Tél : 05 61 28 14 50

# Micro-atelier n°5 « Localisation et caractérisation électrique de défauts dans les VLSI »

La microscopie optique (en lumière visible et infrarouge) est un outil puissant pour localiser les défauts par la face avant comme par la face arrière des composants. L'émission de lumière (EMMI), référence en matière de localisation et la thermographie lock-in infrarouge (LIT) sont de plus en plus utilisées sur les technologies avancées. Couplés à ces systèmes de microscopie, l'utilisation de lasers infrarouges continus, modulés ou pulsés permettent de localiser des défauts de natures très variés (Short, Open résistifs, Soft defect,...) à l'aide des techniques OBIRCH / TIVA, OBIC / LIVA, mais aussi de caractériser la fonctionnalité des produits (DLS / LADA). Enfin pour une caractérisation précise du fonctionnement dynamique des circuits intégrés, des techniques de micro-probing, par capture ponctuelle de photons (TRE / PICA) ou par faisceaux lasers réfléchis (LVI / LVP) peuvent être utilisées. Les outils basés sur les faisceaux d'électrons ont également leur place pour le probing interne des technologies sub-microniques tels que l'utilisation de micro-pointes motorisées dans un microscope électronique permettant aussi de travailler sur les techniques EBIC / EBAC.

Nous insisterons particulièrement sur l'émulation électrique des circuits qui peut être statique, pseudo-statique (en s'arrêtant sur un vecteur de test) et dynamique (en bouclant sur les vecteurs de test choisis). Le groupe de travail sur les « Techniques Optiques Dynamiques / LVI » sera sollicité afin de présenter les avancées sur le sujet.

#### 16h00 - 17h30

### Animateurs :

#### Jérémie DHENNIN ELEMCA - Toulouse jeremie.dhennin@elemca.com

Tél : 05 61 28 25 55

#### Djemel LELLOUCHI ELEMCA - Toulouse diemel lellouchi@elemca.co

djemel.lellouchi@elemca.com Tél : 05 61 27 32 40

### Clovis LATASTE

ELEMCA - Toulouse clovis.lataste@elemca.com Tél : 06 69 46 31 01

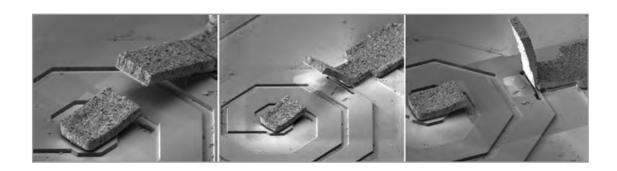

# Micro-atelier n°6 « Analyse de défaillances des MEMs et capteurs physiques ou chimiques »

Les MEMS sont par définition des systèmes multiphysiques, la complexité de ces objets génère donc une difficulté supplémentaire pour l'analyse de défaillance. Ainsi, ce micro-atelier sera dédié à la présentation de techniques ou de résultats d'analyses de défaillance, en particulier pour lesquelles il aura été nécessaire de faire preuve d'inventivité dans la démarche (détournement de systèmes prévus initialement pour un autre type de composant, mise au point d'une nouvelle technique de caractérisation, adaptation particulière du flot d'analyse).

A titre d'exemple, on peut citer les problématiques liées à la caractérisation des couches de fonctionnalisation de surface (application microfluidique ou anti-stiction sur MEMS inertiels), les nouvelles techniques de quantification de l'herméticité des packages, ou bien les difficultés lors de l'analyse de défaillance liées à la présence de plus en plus fréquente d'un ASIC de contrôle sur le même substrat que le MEMS.

## VENDREDI I O JUIN

#### 10h30 - 12h00

#### Animateurs:

#### Pierre LEBOSSE THALES C&S - Toulouse pierre.lebosse@thalesgroup.com Tél: 05 61 28 23 43

# Micro-atelier n°7 « Fiabilité dynamique »

Depuis plusieurs décennies, la mise en œuvre d'essais de vieillissement pour s'assurer de la fiabilité des composants électroniques s'est bornée à une activation minimaliste dans un environnement haute température.

L'évolution des DSM, de leur complexité et de leurs modes de défaillance nécessite de réviser certaines stratégies sur les méthodologies de vieillissement de ces composants.

La mise en œuvre de mécanismes de défaillance type HCl ou NBTI nécessite par exemple une activation dynamique et même dans certains cas une polarisation à basse température, l'objectif étant pour l'assurance de l'utilisateur final d'être le plus proche possible de l'application d'utilisation.

Le mode de vieillissement « Test as you fly » devenant de plus en plus complexe à réaliser sur des composants récents, l'objectif de ce micro-atelier est de présenter les solutions et stratégies choisies par les différents laboratoires et industriels pour mener à bien ces essais et partager sur l'évolution de la complexité de cette mise en œuvre.

# **INSCRIPTIONS: INFORMATIONS GÉNÉRALES**

#### INFORMATIONS PRATIQUES

Site et coordonnées : Au bord de l'océan, séparé uniquement par une dune, sur la côte des Landes, dans une région très

' nature " du Pays Basque, formule résidentielle dans le Club Belambra « Les Tuquets » de Seignosse -

Hossegor en logements de décoration contemporaine et fonctionnelle, accès WiFi.

Transport/Accès : En avion, aéroport de Biarritz à 40 km, aéroport de Bordeaux Mérignac à 170 km.

En train, gare de Dax à 38 km.

En voiture, A63, sortie 10, suivre N10, puis D810 (Coord. GPS lat.: 43.70466 GPS lon.: - 1.432771)

Accueil sur site : Le secrétariat ANADEF sera ouvert

le lundi 6 juin 2016 de 18h00 à 21h00

le mardi 7 juin 2016 à partir de 8h00 et aux heures d'ouverture de l'Atelier.

CONTACT

Votre contact pour toute information concernant votre inscription : Véronique LHEUREUX

ADERA Service - 162, avenue Albert Schweitzer- CS 60040 - 33608 Pessac Cedex

registration@adera.fr - Tél : 05 56 15 80 03 - Fax : 05 56 15 11 60

#### MODALITES ET DROITS D'INSCRIPTIONS

- L'inscription à l'Atelier s'effectue en ligne via le site www.anadef.fr. Elle est nominative. Aucune inscription partagée ne sera acceptée.

- Le montant de la participation inclut par jour :

- Hébergement (1 nuit) / restauration (petit-déjeuner, pauses, déjeuner et dîner)

Participation à la conférence

- · Documentation, CD ROM, actes et liste des participants

- Un tarif préférentiel (indiqué ci-dessous) est accordé aux membres ANADEF à jour de leur cotisation 2016.

- Un tarif dégressif sera appliqué pour l'inscription de 2 participants appartenant à la même entreprise et travaillant sur le même site.

### L'inscription à l'ATELIER 2016 peut être effectuée au titre de la formation continue,

La formation est conventionnée par ADERA- organisme de formation enregistré sous le n° de déclaration d'activité formation 72 33 06982 33 L'inscription à la formation inclut la participation aux sessions plénières des 4 journées de l'Atelier, non dissociables.

> Membre ANADEF Non membre - ANADEF

1560 € TTC 1944 € TTC 1ère inscription 2ème inscription 1404 € TTC 1800 € TTC Formule tout compris : forfait hébergement, participation à la conférence, documentation.

- Date limite d'inscription : Les bulletins d'inscription devront parvenir à l'ADERA au plus tard le 13 mai 2016. Passée cette date, la réservation hôtelière n'est pas garantie sur le site de l'Atelier.

- Une confirmation d'inscription sera adressée à chaque participant.

- Assurez-vous qu'apparaît sur votre moyen de paiement la mention "Inscription à l'Atelier 2016" ainsi que le nom du participant et celui de sa société ou organisme.

- L'accès à l'Atelier sera réservé aux participants ayant acquitté leurs droits d'inscription ou finalisé leur dossier au titre de la formation (convention de formation signée).

Annulation/Remboursement: Toute annulation doit être faite par écrit ou courrier électronique. Si l'annulation parvient à l'ADERA avant le 12 mai 2016, 160 € HT de frais de dossier seront retenus. Aucun remboursement ne sera effectué à partir du 13 mai 2016.

# **Association ANADEF**

Depuis plus de 20 ans, dans un cadre assez peu formel, se réunissent les principaux laboratoires et sociétés du domaine de l'électronique. Afin d'améliorer notre fonctionnement et d'offrir de meilleurs services, nous sommes passés en association.

Les métiers de l'analyse de défaillance des composants et sous-ensembles électroniques, ainsi que celui de la qualification des composants, dans lesquels nous évoluons, sont en perpétuelle évolution. Néanmoins ces métiers sont limités dans chaque entreprise à un petit groupe de personnes. Les investissements, tant en matériel qu'en formation, sont coûteux, et faire le bon choix est essentiel tant pour réaliser directement que pour sous-traiter. L'isolement ne permet pas de faire face rapidement et à faible coût aux nouveaux problèmes, alors qu'un travail de groupe basé sur l'échange et le partage des connaissances permet d'y remédier.

Parmi les principales actions réalisées :

- L'évaluation de techniques nouvelles ou de nouveaux équipements

- · La mise au point de méthodes d'essais, des comparaisons inter-labos

- Le partage technique des expériences

- La création d'un réseau Intranet réservé à nos membres et associé au Site Web (www.anadef.org)

L'appartenance à notre association est le meilleur moyen d'enrichir à la fois ses compétences et ses relations professionnelles ce qui offre alors de multiples possibilités : accès formel ou informel à l'expert du domaine, réalisation d'un type d'essai particulier, organisation de coopérations dans le cadre de programmes français ou européens.

# **COMITÉ SCIENTIFIQUE**

Marise BAFLEUR LAAS - Toulouse

Jeremy DHENNIN

Guillaume BASCOUL INTRASPEC Technologies - Toulouse

Frédéric BOURCIER

CNES - Toulouse

Dominique CARISETTI

THALES R&T - Palaiseau

Vanessa CHAZAL

THALES C&S - Toulouse

Lionel DANTAS de MORAIS

SOFRADIR - Veurey Voroize

Yannick DESHAYES

IMS - Université de Bordeaux

Frédéric DULONDEL

SAGEM Défense sécurité - Eragny

Hélène FREMONT

IMS - Université de Bordeaux

ELEMCA - Toulouse

Matthieu GLEIZES MBDA France - Le Plessis Robinson

Françoise GONNET THALES R&T - Palaiseau

Gérald GUIBAUD THALES C&S - Toulouse

Gérald HALLER ST Microelectronics - Rousset

Sylvie HEUDE-VERNEYRE AIRBUS D&S - Elancourt

Fulvio INFANTE INTRASPEC Technologies - Toulouse

Nathalie LABAT IMS - Université de Bordeaux

Clovis LATASTE ELEMCA - Toulouse

Suzel LAVAGNE

THALES C&S - Toulouse

Pierre LEBOSSE

THALES C&S - Toulouse

Djemel LELLOUCHI

ELEMCA - Toulouse

David LOHIER HIREX Engineering - Toulouse

Olivier MAIRE AIRBUS Group Innovations – Suresnes

Christian MOREAU DGA - Maîtrise de l'Information - Bruz

Catherine MUNIER AIRBUS Group Innovations - Suresnes

Thierry PARASSIN ST Microelectronics - Crolles

Julien PERRAUD THALES R&T - Palaiseau

Cécile PLOUZEAU RENAULT - Guyancourt

Pascal RETAILLEAU MBDA France - Le Plessis-Robinson

**Dominique TALBOURDET** EDF R&D - Moret-sur-Loing

Kevin SANCHEZCNES - ToulouseClaire VACHERULIS - Veurey VoroiseAlain WISLEZTHALES C&S - Toulouse

#### Coordination technique de l'atelier :

Nathalie LABAT - IMS - Université de Bordeaux nathalie.labat@ims-bordeaux.fr - Tél : 05 40 00 65 51

Claire VACHER - ULIS - Veurey Voroize c.vacher@ulis-ir.com - Tél : 04 76 53 68 17

Jean-Marie CHOPIN - ANADEF France

jeanmarie.chopin@wanadoo.fr - Tél: 05 61 37 16 63

Jean-Claude HUBERT - ANADEF France

jcmad.hubert@wanadoo.fr - Tél : 09 71 40 72 74

#### **OBJECTIFS DE L'ATELIER**

1 Faire se rencontrer et dialoguer de façon informelle tous ceux (fabricants de composants, équipementiers, laboratoires d'analyse & universitaires) qui ont en commun le souci de comprendre les mécanismes de défaillance afin de mieux maîtriser les choix de composants en fonction des conditions d'applications (profil de mission) et des objectifs de fiabilité.

L'atelier est le lieu privilégié pour discuter des problèmes concrets qui se posent aux utilisateurs de composants. Il permet d'aborder les cas résolus ou non, de comparer les approches ou les méthodologies et de rapprocher les utilisateurs des fabricants.

- Répondre aux attentes des participants à savoir :

- Elargissement du domaine d'activité (aller au-delà des techniques d'analyse)

- Prise en compte des exigences du marché et des contraintes économiques

- Partage d'expériences

- Rationalisation des démarches/approches

- Développement des contacts informels.

- 3 Promouvoir un réseau de spécialistes via l'association ANADEF.

- 4 Le programme de l'Atelier propose une formation qui fournit des bases de connaissances pour une parfaite compréhension des exposés théoriques présentés au cours des sessions. La formation se répartit sur quatre modules appelés Tutoriels.

# CARACTÉRISTIQUES DU 15ème ATELIER

2016! 15ème édition de l'ATELIER ANADEF! Au rythme d'un Atelier ANADEF tous les deux ans et donc depuis 30 ans, cette 15éme édition est plus que jamais incontournable pour les spécialistes de l'Analyse de Défaillance de composants électroniques et pour tous ceux qui cherchent à comprendre tel mécanisme de défaillance ou bien tout simplement découvrir.

Le comité scientifique, avec comme objectif de privilégier les échanges et le réseau, a préparé un programme renouvelé alliant sessions plénières, destinées à faire un état de l'art des problématiques rencontrées dans nos métiers, et micro-ateliers qui vous permettront d'approfondir ces sujets. Pour cette édition 2016, nous vous proposons certaines thématiques récurrentes, les passifs, le VLSI, la puissance, les technologies d'interconnexion mais aussi de nouveaux thèmes comme l'optoélectronique, les MEMS, la fiabilité dynamique, ... Les tutoriels, plébiscités par les participants lors des précédentes éditions, sont également reconduits avec des thèmes nouveaux. Nous avons œuvré avec l'ADERA, pour rendre ces tutoriels à nouveau éligibles au titre de la formation.

Le magnifique site de Seignosse nous permet de maintenir la formule « tout compris »: hébergement, restauration et conférences à un prix très attractif.

Toute l'équipe organisatrice souhaite une nouvelle fois réunir le plus grand nombre d'acteurs impliqués dans les mécanismes de défaillance des composants électroniques, des systèmes et des assemblages, qu'ils soient issus de laboratoires industriels, publics, académiques ou fournisseurs d'équipements. Nous souhaitons vous voir très nombreux pour que cet ATELIER 2016 soit une nouvelle fois un moment fort d'échanges, de partage et de convivialité.

Le Président d'ANADEF

Alain WISLEZ